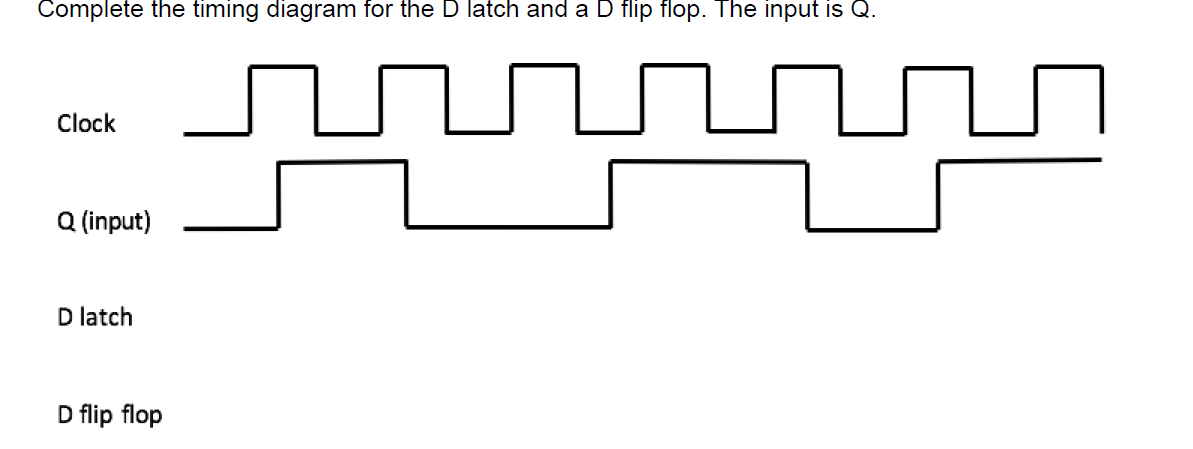

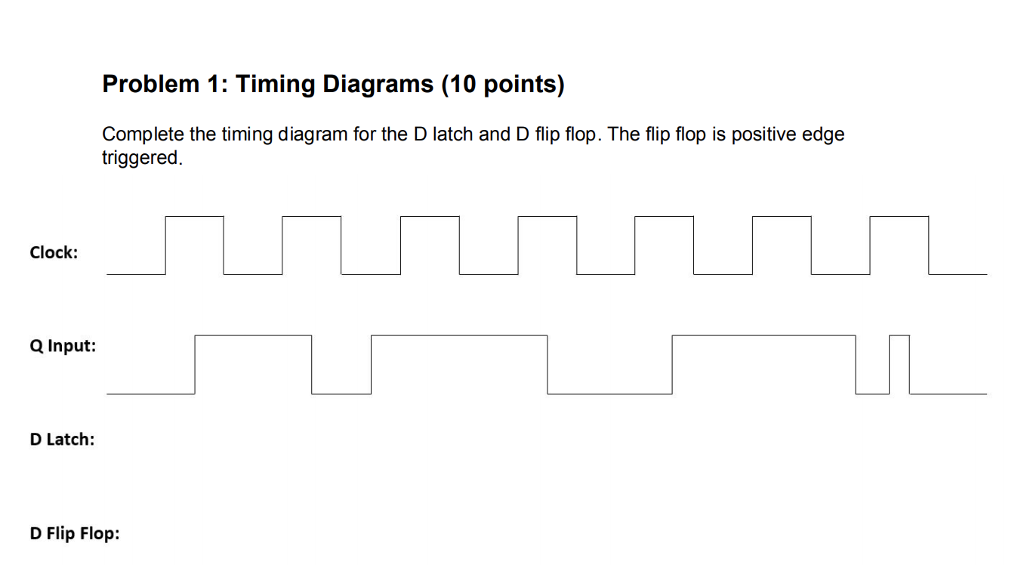

45 d latch timing diagram

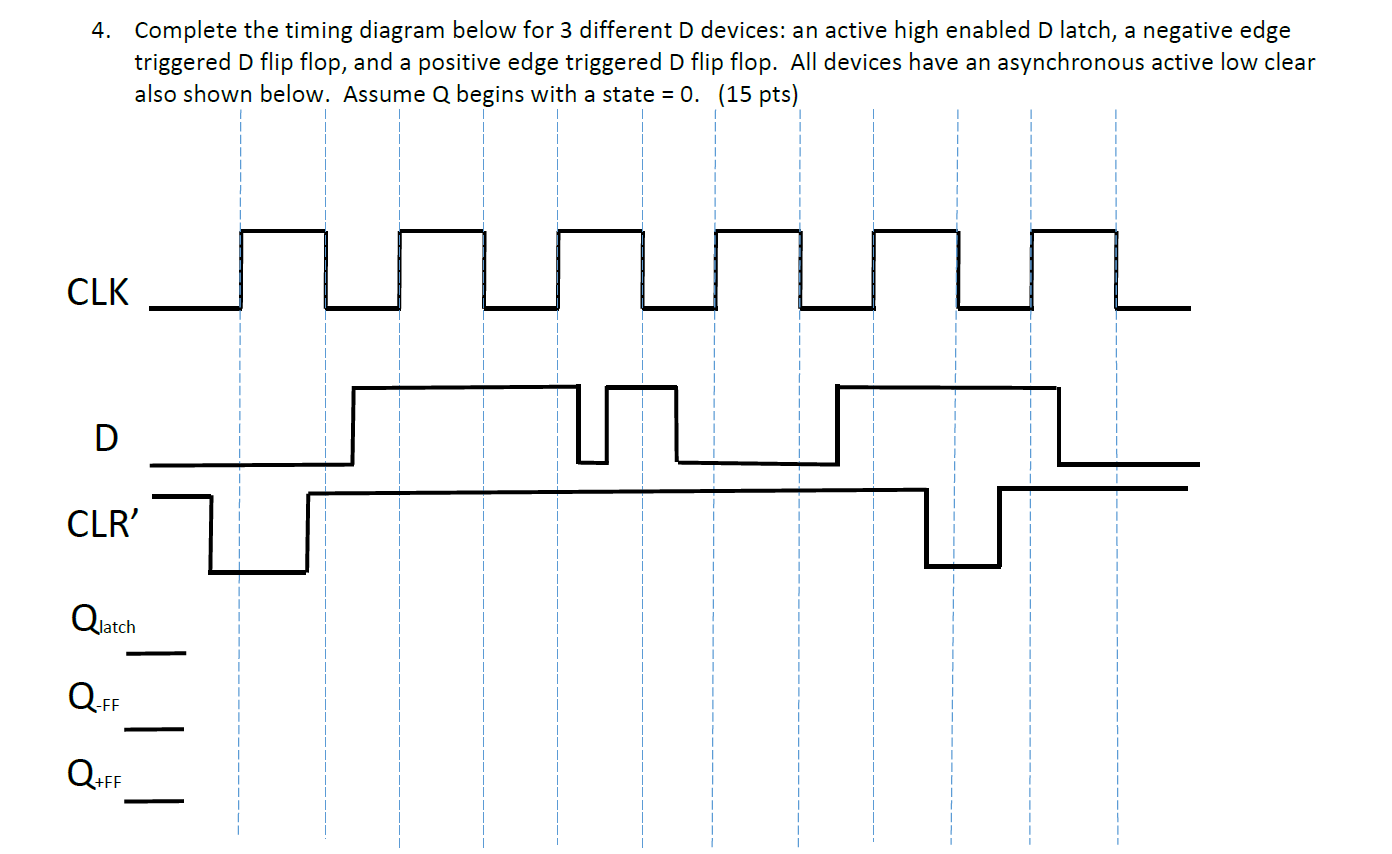

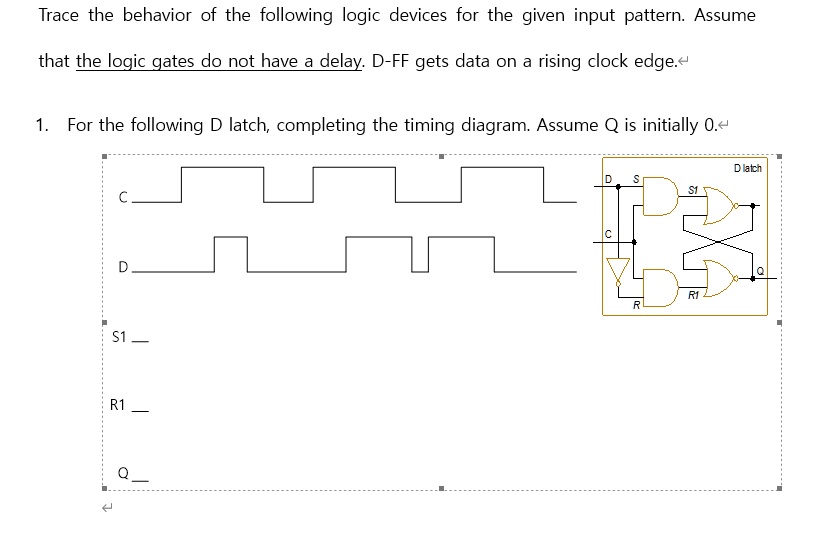

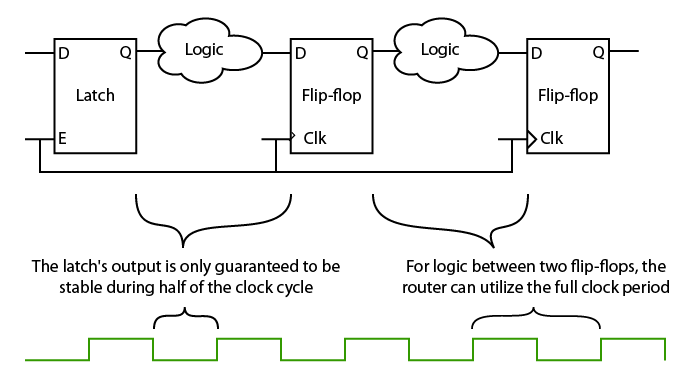

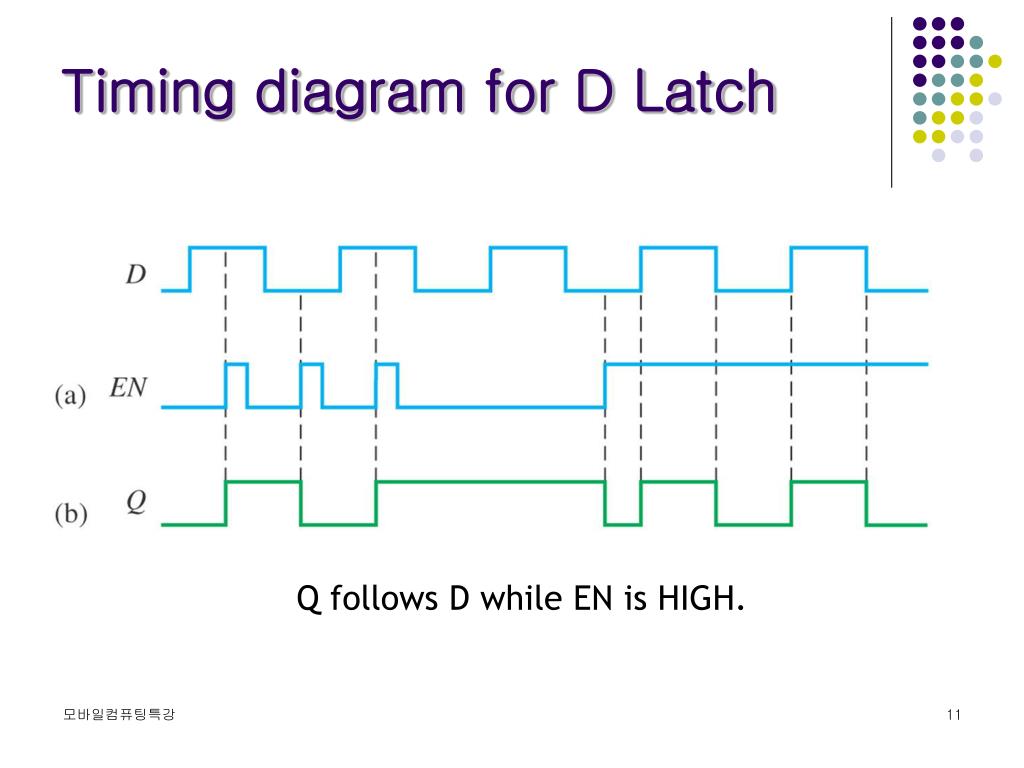

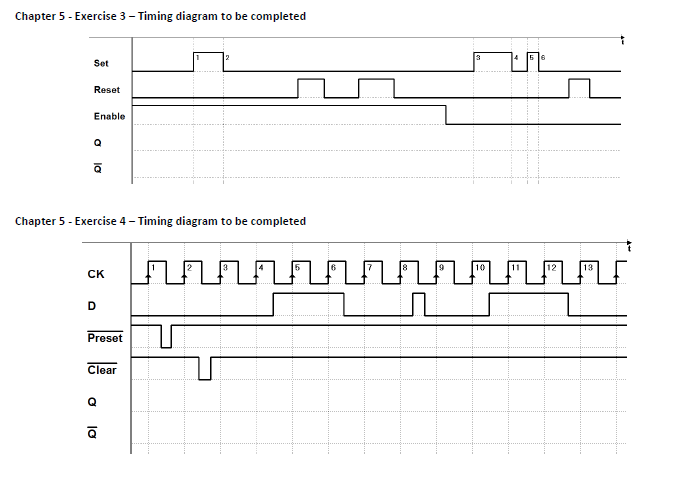

D-Latch AND D-FLIP FLOP (Introduction) : VLSI ... The D latch is used to capture, or 'latch' the logic level which is present on the Data line when the clock input is high. If the data on the D line changes state while the clock pulse is high, then the output, Q, follows the input, D. When the CLK input falls to logic 0, the last state of the D input is trapped and held in the latch. Timing diagram PDF 7. Latches and Flip-Flops Chapter 7 - Latches and Flip-Flops Page 3 of 18 a 0. When both inputs are de-asserted, the SR latch maintains its previous state. Previous to t1, Q has the value 1, so at t1, Q remains at a 1. Similarly, previous to t3, Q has the value 0, so at t3, Q remains at a 0. If both S' and R' are asserted, then both Q and Q' are equal to 1 as shown at time t4.If one of the input signals is

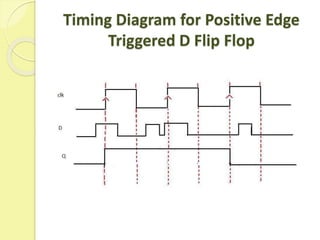

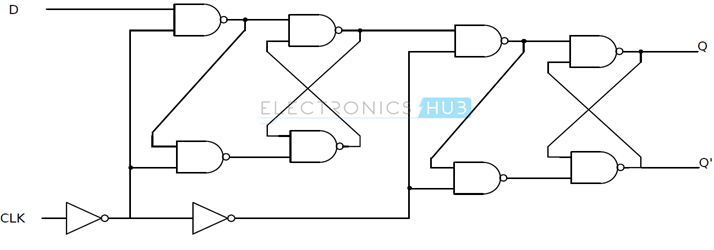

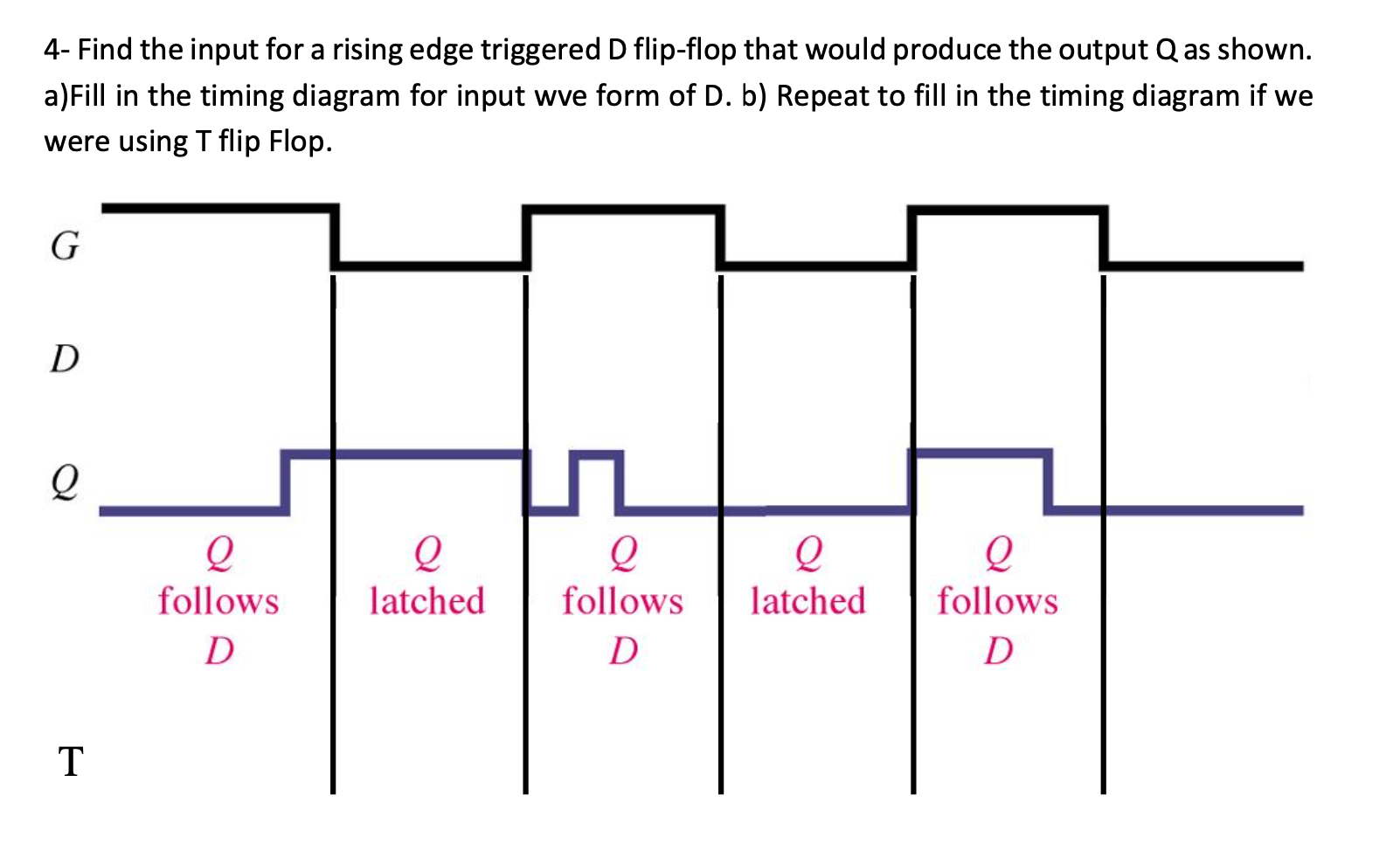

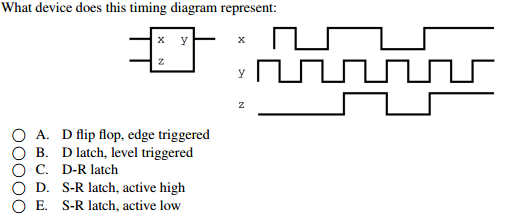

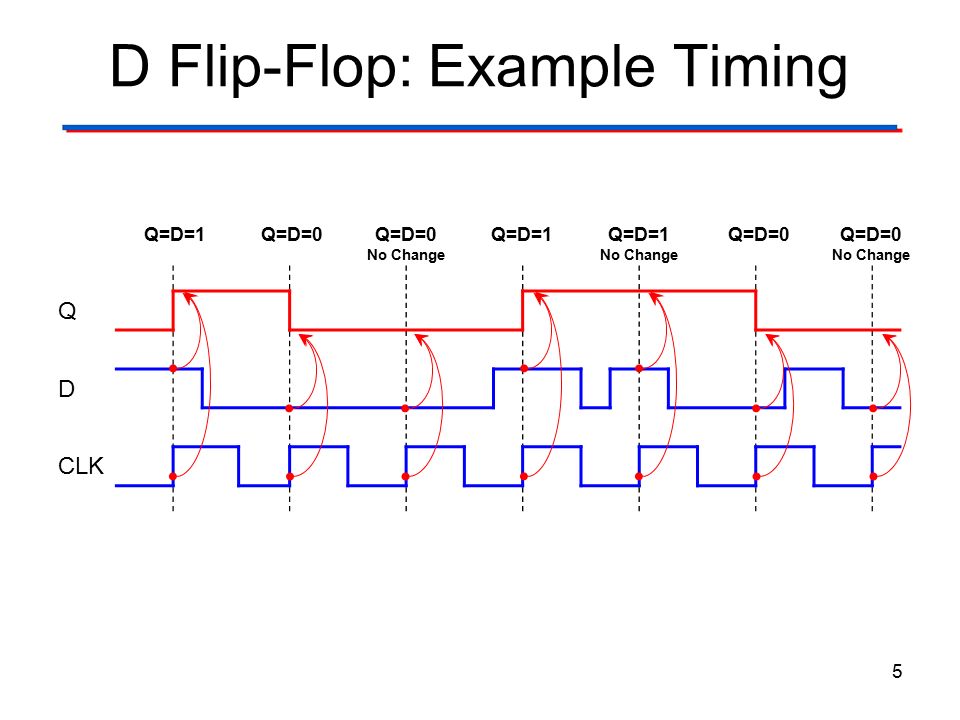

D Flip-Flop Circuit Diagram: Working & Truth Table Explained Thus, D flip-flop is a controlled Bi-stable latch where the clock signal is the control signal. Again, this gets divided into positive edge triggered D flip flop and negative edge triggered D flip-flop. Thus, the output has two stable states based on the inputs which have been discussed below. Truth table of D Flip-Flop:

D latch timing diagram

Answered: 2. TIMING DIAGRAM Positive… | bartleby TIMING DIAGRAM Positive Level-clocked D Latch CLK D. 2. TIMING DIAGRAM Positive Level-clocked D Latch CLK D. Question. thumb_up 100%. Transcribed Image Text: 2. TIMING DIAGRAM Positive Level-clocked D Latch CLK D Expert Solution. Want to see the full answer? Check out a sample Q&A here. D Type Flip-flops - Learn About Electronics The name Data Latch refers to a D Type flip-flop that is level triggered, as the data (1 or 0) appearing at D can be held or 'latched' at any time whilst the CK input is at a high level (logic 1). As can be seen from the timing diagram shown in Fig 5.3.2, if the data at D changes during this time, the Q output assumes the same logic level as the D. Gated D Latch Timing Diagram - schematron.org The Gated D Latch Timing Diagram. February 6, ECE A - Digital Design Principles 28 The Edge Triggered D Flip-Flop The D Flip-Flop (cont) State Diagram 1 0 D = 0 D = 1 D = 1 D = 0. February 6, ECE A - Digital Design Principles 32 The Master-Slave D Flip-Flop.

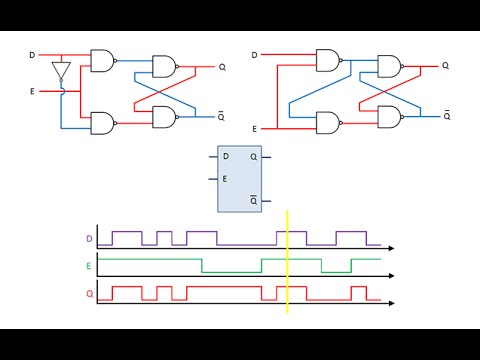

D latch timing diagram. D Flip Flop (D Latch): What is it? (Truth Table & Timing ... This single input is called data input and it is labeled with D. This is why this type of single input Flip flop is known as a D-Flip Flop or D Latch. The basic logical representation (i.e. circuit diagram) of a D-flip flop is shown below. A D latch can be gated. These types of D latches are known as gated D latches. Solved D Latch Timing Diagram The figure shown below ... D Latch Timing Diagram The figure shown below represents the timing diagram for four input signals, R-bar, S-bar, D, and clock going into a rising edge triggered D-latch. (The latch is not pictured.) The vertical dotted lines represent the moments where one of the inputs is transitioning between logic levels. Timing diagram of flip flop and d-latch | Physics Forums Indicate in the provided timing diagram the behavior of the output of the flip-flop and the latch (q_mick and q_keith) as well as the behavior of the output bus between the indicated "start" and "end" times. Use the symbol "Z" to denote the state of the output bus when it is in the high impedance (tri-state value). PDF Overview - University of Washington Edge-triggered D Master-slave Timing diagrams T flip-flops and SR latches CSE370, Lecture 14 2 The D latch Output depends on clock Clock high: Input passes to output Clock low: Latch holds its output Latch are level sensitive and transparent D Q Q CLK Input Output Output CLK D Q latch

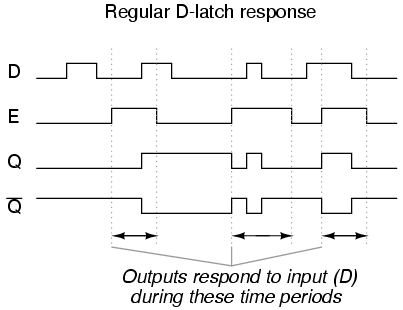

How to draw timing diagram for D Latch and D Flip-flop ... Timing diagram for D flop are explained in this video, if you have any questions please feel free to comment below, I will respond back within 24 hrs Verilog D Latch - javatpoint The D latch is essentially a modification of the gated SR latch. The following image shows the parameters of the D latch in Verilog. The input D is the data to be stored. The input G is used to control the storing. The outputs Q and Qn are the stored data and the complement of the stored data, respectively. Example. In this example, we have a latch with three inputs and one output. Edge-triggered Latches: Flip-Flops | Multivibrators ... Let's compare timing diagrams for a normal D latch versus one that is edge-triggered: In the first timing diagram, the outputs respond to input D whenever the enable (E) input is high, for however long it remains high. When the enable signal falls back to a low state, the circuit remains latched. PDF Overview The D latch - University of Washington #Edge-triggered D #Master-slave " Timing diagrams 2 The D latch! Output depends on clock " Clock high: Input passes to output " Clock low: Latch holds its output! Latch are level sensitive and transparent DQ Q CLK Input Output Output CLK D Qlatch CSE370, Lecture 153 The D flip-flop! Input sampled at clock edge " Rising edge: Input passes to output

The D Latch | Multivibrators | Electronics Textbook The D latch is nothing more than a gated S-R latch with an inverter added to make R the complement (inverse) of S. Let's explore the ladder logic equivalent of a D latch, modified from the basic ladder diagram of an S-R latch: An application for the D latch is a 1-bit memory circuit. flipflop - SR latch timing diagram or waveform with delay ... In the first timing diagram, when S becomes 1, after 10ns QN becomes 0, and 10ns later Q becomes 1. Now, draw the S-R latch with NOR gates, write initial values near corresponding letters (S=0, R=0, Q=0, QN=1), change S to 1, and try to understand what changes you see. If you struggle, look at the timing diagram you shared. PDF Chapter Vii Sequential Systems - Latches & Registers TIMING DIAGRAMS SEQUENTIAL SYSTEMS •LATCHES-SR LATCH -NOR GATES-SR LATCH W/ CONTROL-D LATCH • Timing diagrams allow you to see how a sequential system changes with time using different inputs. • For instance, a timing diagram for a D latch might look like the following. D Enable Q Q Time CSE140: D Latch & D Flip Flop - YouTube Visit for extra study notesUniversity of California, San DiegoCSE 140 - Digital System Design

Flip Flop Timing Diagram - U Wiring D-latch is a level Triggering device while D Flip Flop is an Edge triggering device. Slide 3 of 7. J corresponds The timing diagram for the negatively triggered JK flip-flop. 526 shows a timing diagram describing the action of the basic RS Latch for logic changes at R and S. Symbol for the JK flip-flop.

SR-Latch and D-Latch - realdigital.org D-Latch circuit. A timing diagram for the D latch is shown below in Fig. 4. Note that when the Gate input is asserted, the output Q simply follows the input. But when the Gate input is not asserted, the output remembers the value present at D at the time the Gate signal was de-asserted. Figure 4. D-Latch timing. Important Ideas

Basics of latch timing - VLSI UNIVERSE Positive level-sensitive latch: A positive level-sensitive latch follows the input data signal when enable is '1' and keeps its output when the data when it is '0'. Figure 1 below shows the symbol and the timing waveforms for a latch. As can be seen, whenever enable is '1', out follows the data input. And when enable in '0', out remains the same.

Timing Diagram D Flip Flop - U Wiring Timing diagram for D flop are explained in this video if you have any questions please feel free to comment below I will respond back within 24 hrs. JK Master-Slave Flip-Flop timing diagram. In D flip-flop if D 1 then S 1 and R 0 hence the latch is set on the other hand if D 0 then S 0 and R 1 hence the latch is reset.

Flip-Flops and Latches - Northwestern Mechatronics Wiki The timing diagram for the negatively triggered JK flip-flop: Latches. Latches are similar to flip-flops, but instead of being edge triggered, they are level triggered.. The most common type of latch is the D latch.While CK is high, Q will take whatever value D is at. When CK is low, Q will latch onto the last value it had before CK went low, and hold it until CK goes high again.

PDF Latch Modeling for Statistical Timing Analysis timing diagram and structure of transparent latch are reviewed, with traditional latch delay model. A new point of view for latch working mode based on a 3-D analysis is proposed in Section III. Section IV presents our new latch delay model taking into account variations such as data slew, clock slew among others Statistical timing analysis for

D Latch - Online Digital Electronics Course In this situation, the latch is said to be "open" and the path from the input D to the output Q is "transparent". Thus the circuit is also known as a transparent latch. When E is 0, the latch is disabled or "closed", and the Q output retains its last value independent of the D input. The truth table and diagram

D Latch Timing Diagram - Electrical Engineering Stack Exchange I've been googling d latch timing diagrams to figure out the above- haven't found it yet but did notice that alot of other d latch timing diagrams look like horizontal lines/box/square wave shapes . latch. Share. Cite. Follow asked Dec 25, 2015 at 21:21. LongApple LongApple.

Overview The D latch - Washington Timing diagrams. □ T flip-flops and SR latches. 2. CSE370, Lecture 14. The D latch. ◇ Output depends on clock. □ Clock high: Input passes to output.

PDF Lecture 11: Sequential Circuit Design - Harvey Mudd College - a.k.a. transparent latch, D latch Flip-flop: edge triggered - A.k.a. master-slave flip-flop, D flip-flop, D register Timing Diagrams - Transparent - Opaque - Edge-trigger D Latch Q Flop clk clk DQ clk D Q (latch) Q (flop) 11: Sequential Circuits 7CMOS VLSI DesignCMOS VLSI Design 4th Ed.

PDF Latches, the D Flip-Flop & Counter Design - UC Santa Barbara The Gated D Latch Timing Diagram. February 6, 2012 ECE 152A - Digital Design Principles 28 The Edge Triggered D Flip-Flop

Sr Flip Flop Timing Diagram - schematron.org • Representation of a set of Clocked RS latch D Flip- Flop. • A D flip-flop can be constructed from an RS flip-flip to allow clocking and. SR Flip Flop and Clocked SR Flip Flop (Digital Electronics)(Hindi) - Duration: 9: physicsanddigitalelectronics , views · Digital Timing Diagram. • Representation of a set of Clocked RS latch D Flip- Flop.

Gated D Latch Timing Diagram - schematron.org The Gated D Latch Timing Diagram. February 6, ECE A - Digital Design Principles 28 The Edge Triggered D Flip-Flop The D Flip-Flop (cont) State Diagram 1 0 D = 0 D = 1 D = 1 D = 0. February 6, ECE A - Digital Design Principles 32 The Master-Slave D Flip-Flop.

D Type Flip-flops - Learn About Electronics The name Data Latch refers to a D Type flip-flop that is level triggered, as the data (1 or 0) appearing at D can be held or 'latched' at any time whilst the CK input is at a high level (logic 1). As can be seen from the timing diagram shown in Fig 5.3.2, if the data at D changes during this time, the Q output assumes the same logic level as the D.

Answered: 2. TIMING DIAGRAM Positive… | bartleby TIMING DIAGRAM Positive Level-clocked D Latch CLK D. 2. TIMING DIAGRAM Positive Level-clocked D Latch CLK D. Question. thumb_up 100%. Transcribed Image Text: 2. TIMING DIAGRAM Positive Level-clocked D Latch CLK D Expert Solution. Want to see the full answer? Check out a sample Q&A here.

![Solved]: 6 Assume Feed Clk D Signals Clocked D Latch Draw O](https://media.cheggcdn.com/media/78a/78ab57a1-ed77-42ac-b378-f5ca568317ab/phptrIIdf.png)

0 Response to "45 d latch timing diagram"

Post a Comment